Driven by the consumer IC market of emerging applications, such as CMOS Image Sensor (CIS), and 8-bit or 16-bit MCU for the controller of Internet of Things (IoT) in Health Care, Smart Energy System or Intelligent Family field, various product types, reference design and development tools and R&D staff training are needed to provide. To response to the prompt demand, the designers need rapid construction structures to come out new cells in a short time and less or even no trainings for new users, an open environment which can be integrated with third party tools to facilitate all design flow and a custom solution to optimize the layout.

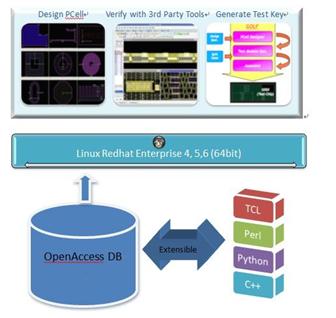

Thus, the IC layout designers need a unified, simple but powerful layout solution to design PCell, run simulation, debug and verify in the same environment to deliver time-to-market and high quality products. GOLF is a Schematic-Driven and OpenAccess-based layout solution that provides the full hierarchical manipulation capability to increase layout productivity up to a maximum of 30X+. GOLF provides a complete solution to design and debug PCell, run 3rd party DRC, LVS or LPE tools and generate test key in an integrated development environment (IDE).

Benefits

- Schematic-Driven Layout (SDL) provides the efficiency of debugging, high layout productivity in an easy-to-use environment

- GUI-based, rich PCell primitive types and parameterized IDE environment to convenience the layout design and reduce the learning curve for new users

- Test Key Layout Generation reduces product time-to-market by guided and parameterized test structures, automated and efficient methodology.

- GOLF's custom layout service completes your layout solution and can increase 10X+~30X+ productivity.

Open environment and extensible architecture

GOLF is an OpenAccess-based layout solution that provides full hierarchical manipulation capability to increase layout productivity up to a maximum of 30X+. GOLF provides comprehensive methodologies which include powerful layout editing and debugging functions, intuitive GUI, flexible customization and extension with TCL/Perl/Python/C++ to enable layout designers to achieve correct-by-construction results.

Intuitively design PCell with parameters in GUI

GOLF provides PCell design, preview, testing, debugging, and documentation in a unified environment. Designing Cell in GOLF is parameterized and step-by-step; just entering parameters for a PCell in GUI instead of programming codes, even the engineers without any programming experience can follow the steps to come out PCells directly. It is based on Anaglobe's patented highly flexible and reusable hierarchical parameterized layout generator.

More than the types that system-predefined, over 40 primitive PCell objects are provided to ease the use of devices and various operators are also supplied for the convenience of device modification or reuse. Special shapes also can be created easily in GUI as well.

Intelligent test key layout generation

Test key layout generator is the solution for test vehicle development by creating reusable and parameterized test structure. Designers only need to input parameters, define split table with or without routing constrains, then the test module can be interactively generated and assembled to place test modules into a single top design. With this solution, the conventional test chip development flow can be changed into an efficient, consistent and automated methodology.

Schematic-Driven layout solution

Anaglobe's GOLF is the worldwide proven layout solution which enabling users to overcome the challenges of today's demand from the volatile market with little or no learning curve. Schematic-based editing and step-by-step guided layout tasks are just accomplished with easy clicks, parameter inputs or intuitive menu accesses.

SDL operates with a hierarchical connectivity model working simultaneously at all levels of the design hierarchy. This capability will alarm connectivity errors as the net is short or open. This makes designers easier to understand the complexity of interactions through the design hierarchy.

SDL also supports one-to-many mapping across multiple hierarchy levels. This allows layout designers to view different layout hierarchies at the same time for efficient net tracing or debugging. The cross probing of hierarchy net tracer and short Indicator can easily highlight the problem net without Place-and- Route (P&R), LVS or LPE. It does significantly reduce efforts and speed up the debugging processes.

Custom layout solution

There is always the gap between the solution of the standard layout tool and problems that users have. With GOLF's customization service, complete layout requirements can be satisfied and productivity can be increased up to 10X+~30X+. One example is to unify the test chip layout with customized P&R and parser in GOLF only that you don't need to switch in various tools, spend time in database transformation any more. There are also other reference customization projects as described below:

- Dummy pattern insertion

- Net checker

- Bump cell placer

- Web-based analysis and inquiry system

- Customized tape-out flow

- Defect inspection flow

Join GOLF customization, then you can spend less and get more.

Conclusion

To shorten the layout cycle and maximize the productivity, GOLF – provided by AnaGlobe (http://www.anaglobe.com/), does address the problems that deep nanometer layouts meet and provides the highly integrated, multi-vendor tool suite for custom and cell-based design and verification .The leading-edge semiconductor foundries or famous design companies do gain from the adoption of GOLF to layout their analog, mixed-signal, logic, embedded memory or RF designs.

Open environment and extensible architecture

DIGITIMES' editorial team was not involved in the creation or production of this content. Companies looking to contribute commercial news or press releases are welcome to contact us.