Global Unichip Corp. (GUC), the advanced ASIC leader, disclosed that its second-generation GLink 2.0 (GUC multi-die interLink) interface, using TSMC 5nm process and TSMC advanced packaging technology for multi-die integration in AI, HPC and Networking applications, has passed full silicon qualification.

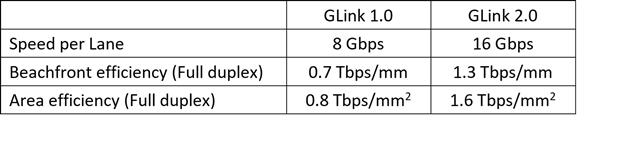

Like its predecessor GLink 1.0, GLink 2.0 supports InFO_oS and all CoWoS types (both silicon and organic interposers). GLink 2.0 is fully backward compatible with GLink 1.0, with similar power consumption while doubling speed per lane, beachfront, and area efficiency. Die edge is the scarcest resource and GLink-2.0 allows the most efficient use of it by transferring 1.3 Tbps of full-duplex traffic per every mm of beachfront. Lead AI & Networking customers adopted GLink 2.0 for their next-generation products and expect mass productions in 2023 and thereafter.

GLink 2.0's power consumption is more than 2 times lower than alternative solutions using ultra-short reach SerDes-based communication through package substrate. For every 10 Tbps of full-duplex traffic, it consumes 10 to 15 W less power than alternative SerDes-based interfaces, and it occupies more than 2 times less area of silicon and beachfront. Serial interfaces (SerDes) consume constant power according to the worst-case data pattern. It always consumes the same power even when traffic is reduced or idle, burning maximal power according to the absolute worst-case traffic scenario. The GLink parallel bus doesn't randomize data; it consumes power proportional to the actual data toggle rate, and even further reduces the toggle rate using Data Bus Inversion (DBI). This allows our customers to burn 10 to 20 times less power in practical workloads vs. SerDes-based links.

GLink IP delivery includes all analog and digital parts; its parallel interface is connected directly to user interfaces or common buses like AXI. Integrated TX and RX Clock Domain Crossing (CDC) FIFOs allow any ratio between transmitter and receiver clock frequencies, increasing system flexibility. GLink includes a Link Training hardware state machine and automatic voltage-temperature changes tracking during normal operation so that the user software is not involved in interface control. GLink has redundant lanes to replace faulty ones during production tests or in the field. The proteanTecs Universal Chip Telemetry (UCT) is integrated into the PHY. It can be used to monitor the signal quality of every physical lane during normal operation, to observe lane degradation due to CoWoS or InFO_oS physical effects, and to support a decision to replace a marginal quality lane with a redundant one in order to prevent system failure and extend the product's life cycle.

The next GLink versions using TSMC 5nm and 3nm technologies will support 2.5 Tbps/mm, error-free full-duplex traffic with similar power consumption, and will be available in Q4, 2021, and Q1, 2022, respectively.

"5G and AI are paving the way for Digital Transformation, i.e., smart connectivity, data center and edge computing/AIoT. The key enablers for Digital Transformation are HPC platform, 2.5D/3D Advanced Packaging, and ASIC & Scalable Processors. GUC just recently announced our HBM3 and GLink-3D solutions. By fully qualifying second-generation GLink 2.0 silicon, GUC is showing a long-term commitment to providing the most competitive advanced package technology total solution for enabling Digital Transformation, including a full set of best-in-class and silicon-proven HBM2E/3 PHY & Controller, GLink 2.5D and 3D die to die interfaces, CoWoS and InFO_oS expertise, electrical and thermal simulations, package design and manufacturing, DFT and production test," explains Dr. Ken Chen, president of GUC.

"We are developing our IPs for integration in a harsh environment of >1000W, many-reticle size ASICs. We tested GLink 2.0 for robust and stable operation in a full spectrum of operating conditions as we learned from our products, and we observed error-free operation in the toughest system operation scenarios. We leverage deep knowledge of TSMC's 2.5D and 3D technology in order to develop the highest bandwidth and the lowest power die-to-die interfaces. We are committed to double bandwidth density every year while keeping power low and reducing latency, enabling CPU, GPU, DPU, AI, and Networking Processors of the future," said Igor Elkanovich, CTO of GUC.

Key GLink 2.0 16 Gbps N5 highlights:

*Full duplex 1.3 Tbps traffic per 1 mm of beachfront

*0.3 pJ/bit (i.e., 0.3W per 1 Tbps of full-duplex traffic)

*Error-free operation in all PVT corners, changing voltage and temperature, and high voltage noise

*PPA advantage over SerDes links using package substrate

-More than 2 times lower power consumption

-More than 2 times smaller silicon area and beachfront

-Error-free, no BER, no FEC, no Link, and Transaction Layers

-2-3 times lower end-to-end latency

*Supports InFO_oS and all CoWoS types (both silicon and organic interposers)

*Low area/power overhead for high throughput interconnect enables efficient multi-die CoWoS and InFO_oS solutions up to 2500 mm2

Learn More about GUC's GLink IP with InFO/CoWoS Total Solution

About GUC

Global Unichip Corp. (GUC) is the Advanced ASIC Leader, who provides the semiconductor industry with leading IC implementation and SoC manufacturing services, using advanced process and packaging technology. Based in Hsin-chu Taiwan, GUC has developed a global reputation with a presence in China, Europe, Japan, Korea, and North America. GUC is publicly traded on the Taiwan Stock Exchange under the symbol 3443. For more information, visit www.guc-asic.com

Specification comparisons between GLink 1.0 and 2.0

The GLink 2.0 IP using TSMC 5nm process and 2.5D advanced packaging technology passing full silicon qualification