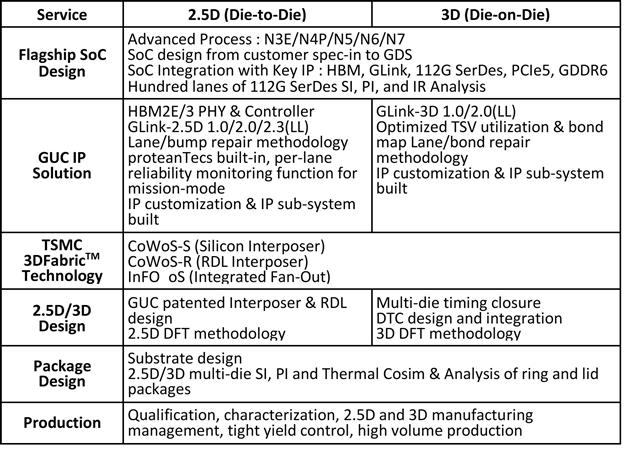

Global Unichip Corp. (GUC), the Advanced ASIC Leader, announces the availability of a platform to shorten design cycles for low-risk, high-yield production of ASICs with TSMC 2.5D and 3D Advanced Packaging Technology (APT). The platform supports TSMC's CoWoS-S, CoWoS-R, and InFO technologies. GUC provides a total solution: silicon-proven interface IPs, CoWoS® and InFO silicon-correlated design, signal and power integrity, thermal simulation flows, and high volume product proven DFT and production tests.

GUC has many years of high-volume production experience of CoWoS-S (silicon interposer) products with HBM using in-house and 3rd party PHY and Controller IPs. InFO design and simulation flows were silicon-correlated using many GLink testchips in N7 and N5 (GLink is GUC die-to-die interface IP family). Recently GUC validated the CoWoS-R (organic interposer) testchip using GUC's 4Gbps HBM2E PHY and Controller IPs, implemented in TSMC N5. Interposer design, layout, signal and power integrity (SI/PI) simulation flows using an organic interposer were correlated with silicon testing results. Now GUC owns a full set of silicon-proven interface IPs, a silicon-correlated design, and simulation flows for all types of TSMC 2.5D technologies. This allows our customers to choose the most optimal solution for any CPU, GPU, AI, HPC and Networking product.

While 2.5D multi-die integration is mature and already widely used by GUC, emerging 3D multi-die integration allows the next level of connection density, power efficiency, and very low latency. GUC leads ASIC industry with GLink die-on-die interface IP using TSMC's N5 and N6 processes. The IP design and simulation flows will soon be silicon-validated for different 3D IC packaging.

"In 2021, GUC made a breakthrough by developing next-generation HBM3, GLink-2.5D, GLink-3D IPs as well as validating CoWoS-S/R and InFO design platforms. GUC keeps collaborating with TSMC to reduce the barrier for the most advanced 2.5D and 3D technologies, enabling our customers to develop high performance, cost efficient products and to bring them quickly to high volume manufacturing", said Sean Tai, president of GUC. "GUC successfully enabled many AI, HPC, and Networking customer products adopting TSMC CoWoS-S and InFO technologies. With availability of CoWoS-R and 3DIC platforms we provide the most comprehensive design and manufacturing service to our customers."

"We are first in the market with HBM3 PHY and the highest performance HBM3 Controller. We also lead the industry with GLink-2.5D IP for die-to-die interconnect, providing unmatching 2.5 Tbps/mm beachfront efficiency (full duplex) and 0.30 pJ/bit power. These IPs can be used in all types of TSMC's 2.5D platforms. Soon, we will validate GLink-3D at 9 Tbps/mm2 (full duplex) and it will open an era of 3D ASICs", said Igor Elkanovich, CTO of GUC. "The unique combination of in-house IPs, silicon-correlated design flows for all types of TSMC technologies, and high volume production experience allow fast development and production ramp-up of huge scale AI/HPC/Networking products."

To learn more about GUC's HBM3/2E, GLink IP portfolio and InFO_oS, and CoWoS® total solution, please contact your GUC sales representative directly or email guc_sales@guc-asic.com.

GUC provides 2.5D and 3D multi-die APT platform solution for AI, HPC, Networking ASICs