The advantages of NOR flash for embedded applications are well known. It is fast, and it allows software to run and modify its contents highly reliably because it functions in a random access mode, in contrast to the block mode of NAND flash.

Building on these advantages, Spansion has now developed embedded Charge Trap (eCT) technology, an embedded NOR Flash memory based on MirrorBit Charge Trap technology, but modified and optimized for integration with logic. The technology is designed to provide fast access, low power, and a cost-effective solution for system-on-chip (SoC) products that require monolithically integrated Flash memory and high-performance logic.

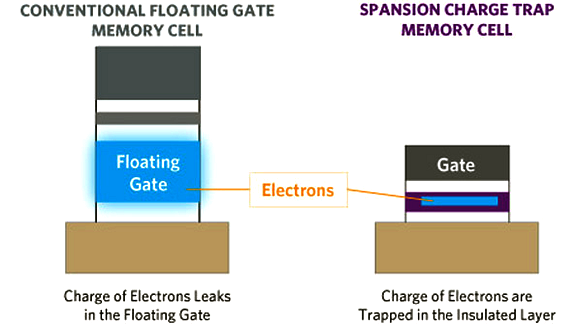

The techniques we utilize for programming and erasing the eCT cell are fundamentally the same as with our MirrorBit NOR Flash technology. The charge-retaining memory stores electric charge in a thin nitride based dielectric (Fig. 1). Spansion's MirrorBit operates at 2 bits per cell, to provide very efficient memory for high-density products, while our eCT technology relies on a single bit per cell. However, the eCT architecture offers advantages in read speed and power consumption. Overall, eCT technology offers a broad temperature range, fast access times (<10ns), and low power. As a memory solution for SoC products, it is highly scalable and optimized for ease of integration with high-performance logic.

The floating-gate tradition

The traditional approach has been to store freely moving electrons in a floating-gate (Fig. 1), but this has a major disadvantage - it is prone to electron leakage. Charge Trap Technology, on the other hand, uses a non-conductive nitride storage layer to trap electrons in place. Charge Trap technology is simpler, more planar and thus easier to manufacture and integrate with logic. What we might call its enhanced "manufacturability" results in a more reliable product, one that is also higher in performance.

Targeted applications

The applications of Spansion eCT technology are quite broad and diverse. The technology can be easily ported to different process technologies and used with a wide array microcontrollers or system-on-chip designs for a host of end products that serve automotive, consumer and industrial applications.

Importantly, eCT technology has a key role to play in extending the roadmap of Spansion's Programmable System Solutions (PSS), which combine Flash memory with configurable logic to enhance processing performance for applications that are memory, processing and MIPS intensive.

The first product in this new PSS portfolio was the Spansion Acoustic Coprocessor, which we announced back in June 2012. The Spansion Acoustic Coprocessor comprises custom-designed logic and high-speed memory to accelerate and optimize voice-enabled human machine interfaces, while offloading the acoustic processing workload from a conventional CPU.

Logic and Flash: A balancing act

Crucially, what eCT offers is a compelling solution to the problems the industry is now encountering as it attempts to scale embedded memory with logic. Many of today's MCUs and SoCs integrate some non-volatile memory; however, suppliers are not able to scale the memory cells and their performance in a way that keeps pace with advancements in logic design.

Leveraging its long history in non-volatile memory and the more than 10 years it has spent in developing Charge Trap Technology for discrete Flash memory, Spansion is responding to the scaling dilemma by enabling embedded Charge Trap technology for embedded MCUs and SoCs. Spansion is leading the industry in restoring the balance between logic and Flash.

(Article Source: Saied Tehrani, CTO, Spansion Inc.)

Figure 1. Spansion's embedded Charge Trap (eCT) NOR technology traps electrons in the insulated layer, allowing more compact storage cells.

DIGITIMES' editorial team was not involved in the creation or production of this content. Companies looking to contribute commercial news or press releases are welcome to contact us.